ESP32-C2 Series SoC Faults Documentation

Espressif has released the whitepaper called ESP32-C2 Series SoC Faults.

This document in pdf format describes a bug document published by Espressif Systems. This document describes bugs and fixes available in ESP8684 series chip products. The main topics of the document are:

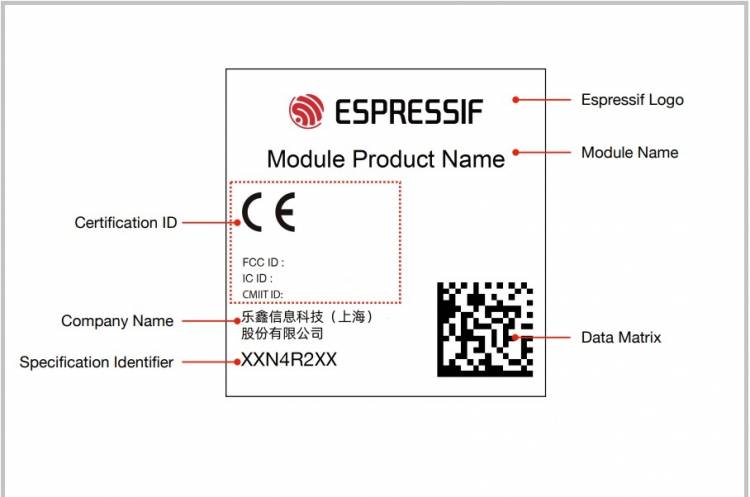

1. Chip Identification: This section provides information on how to check the current version of the document. It is recommended to check the latest document version with a link or QR code.

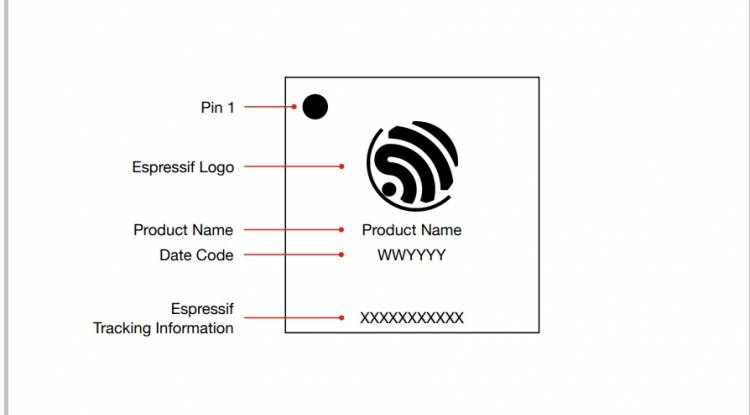

2. Chip Revision: Espressif introduces a new chip revision numbering scheme, the vM.X numbering scheme. This numbering scheme is used to denote major and minor revisions of chip products. It also explains in detail how chip revisions are defined and determined.

3. Additional Methods: This section states that some bugs do not need to be fixed with a new chip revision. These errors can be identified by methods such as the date code or the PW number on the product label.

4. Bug Descriptions: This section describes bug fixes that are the main topic of the document. An example of an error with the crystal is given and how this error can be resolved is explained.

5. Related Documentation and Resources: Documentation and resources related to ESP8684 series products are listed. These documents contain hardware specifications, technical reference guide, hardware design guidelines, and other related information.

6. Revision History: Release dates of different versions of the document and content changes are listed in this section.

The document was prepared to explain to users and developers of ESP8684 series chip products what the errors in these products are, how they can be fixed and how to access relevant resources.

You can access the document at this link:

esp8684_errata_en.pdf (espressif.com)

Brief Information About ESP32-C2:

The ESP32-C2 has a reduced silicon area as it comes in a 4mm x 8266mm QFN package, which is smaller than that of the ESP4. Additionally, the ESP32-C2's ROM code has been optimized to reduce the need for flash capacity, combined with 272 KB of internal SRAM. The ESP32-C2 is powered by Espressif's RISC-V 32-bit single-core processor, which enables the use of RISC-V-based open-source toolchains while also reducing associated costs.